#### **Performance Analysis of GPU-Accelerated Applications** using the Roofline Model

GTC 2019, San Jose

**Charlene Yang Application Performance Specialist NERSC, LBNL** cjyang@lbl.gov

**Samuel Williams Senior Staff Scientist CRD**, **LBNL** swwilliams@lbl.gov

# You just bought a \$10,000 throughput-optimized GPU! Are you making good use of

# Are you making good use of your investment?

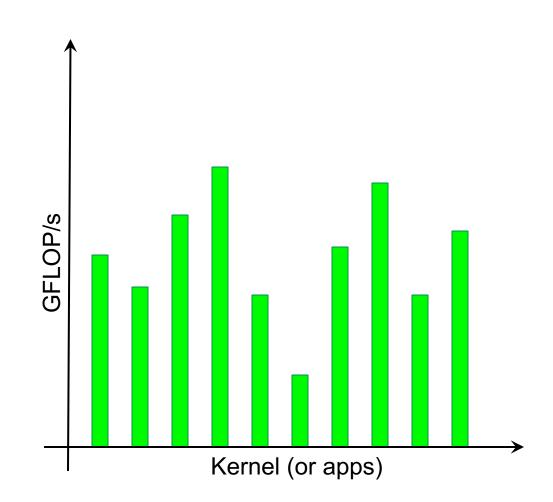

### You could just run benchmarks

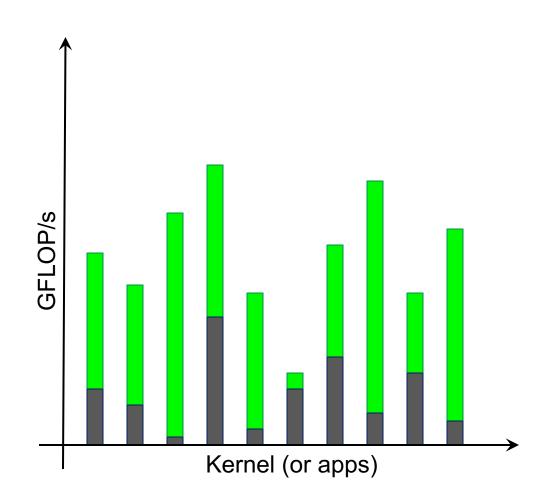

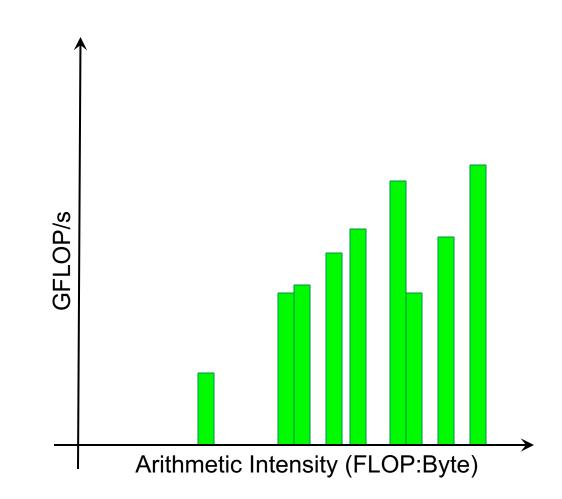

- Imagine a mix of benchmarks or kernels...

- GFLOP/s alone may not be particularly insightful

- Moreover, speedup relative to a Xeon may seem random

# Making good use of your GPU?

- 1. Are you operating it in the throughput-limited regime?

- Not sensitive to Amdahl effects

- Not sensitive to D2H/H2D transfers  $\bigcirc$

- Not sensitive to launch overheads  $\bigcirc$

- Not sensitive to latencies  $\bigcirc$

- 2. If in the throughput-limited regime, are you making good use of the GPU's compute and bandwidth capabilities?

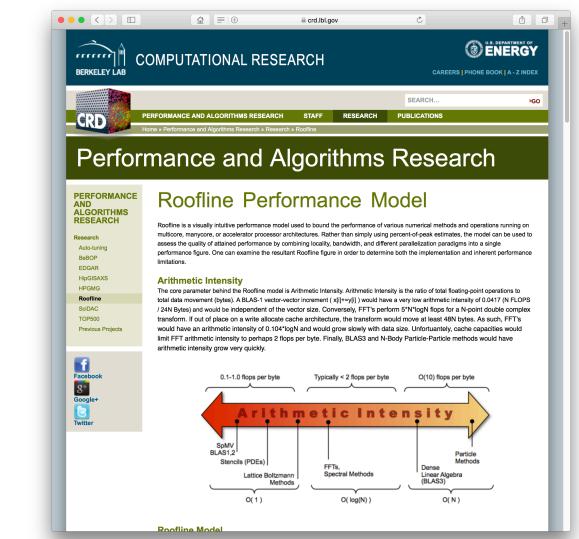

### **The Roofline Model**

- Roofline Model is a throughputoriented performance model

- Premised on the interplay between FLOP/s, bandwidth, and reuse

- Tracks rates not times

- Independent of ISA and architecture (applies to CPUs, GPUs, Google) TPUs, etc...)

https://crd.lbl.gov/departments/computer-science/PAR/research/roofline

Jouppi et al, "In-Datacenter Performance Analysis of a Tensor Processing Unit", ISCA, 2017.

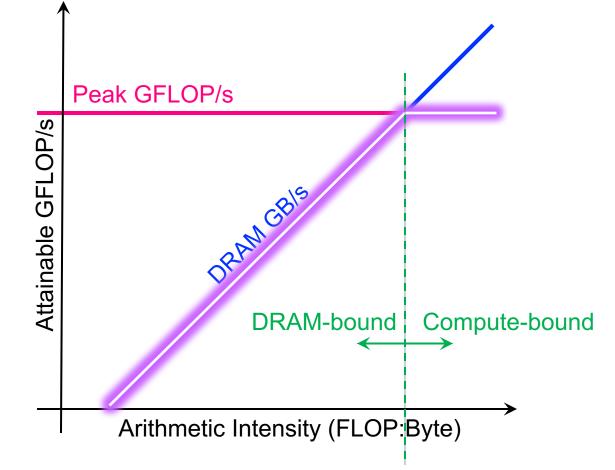

# (DRAM) Roofline

- One could hope to always attain peak performance (GFLOP/s)

- However, finite locality (reuse) and bandwidth limit performance.

- Assume:

- Idealized processor/caches

- Cold start (data in DRAM)

#### Time = max #FLOPs / Peak GFLOP/s #Bytes / Peak GB/s

| (compute,   |           |

|-------------|-----------|

|             | DR<br>(Gl |

| DR<br>(data |           |

#### RAM Bandwidth B/s)

#### **VI** 3)

# (DRAM) Roofline

- One could hope to always attain peak performance (GFLOP/s)

- However, finite locality (reuse) and bandwidth limit performance.

- Assume:

- Idealized processor/caches

- Cold start (data in DRAM)

# GFLOP/s = min AI \* Peak GB/s

Note, Arithmetic Intensity (AI) = FLOPs / Bytes (as presented to DRAM)

| GF<br>(compute, |           |

|-----------------|-----------|

|                 | DR<br>(GI |

| DR<br>(data     |           |

#### RAM Bandwidth B/s)

#### **VI** 3)

#### **Arithmetic Intensity**

- **Arithmetic Intensity** is the most important concept in Roofline.

- Measure of data locality (data reuse)

- Ratio of **Total FLOPs** performed to **Total Bytes** moved

- For the DRAM Roofline...

- Total Bytes to/from DRAM and includes all cache and prefetcher effects Ο

- Can be very different from total loads/stores (bytes requested) due to cache reuse Ο

#### Office of Science

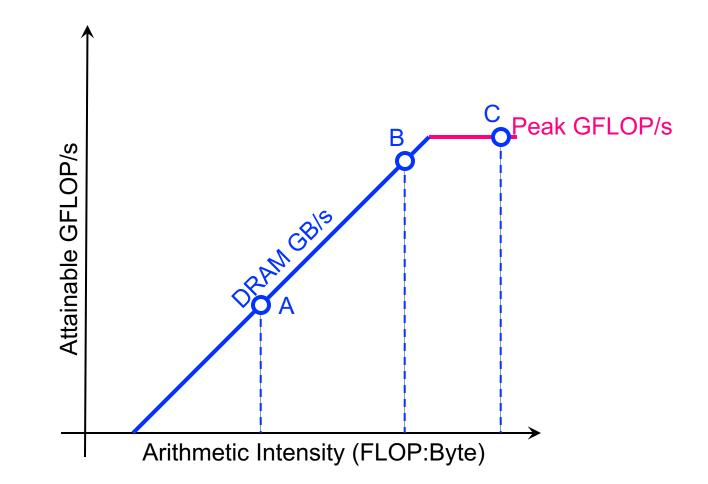

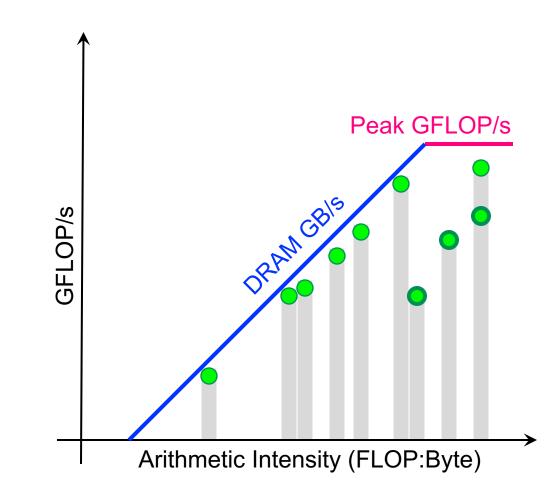

### (DRAM) Roofline

- Plot Roofline bound using Arithmetic Intensity as the x-axis

- Log-log scale makes it easy to doodle, extrapolate performance along Moore's Law, etc...

- Kernels with AI less than machine balance are ultimately DRAM bound (we'll refine this later...)

#### Transition @ AI == Peak Gflop/s / Peak GB/s == 'Machine Balance'

#### Example

- Consider 3 kernels (A,B,C)

- calculate or measure the Arithmetic Intensity for each

- Determine the Roofline intercept for each kernel

- kernels A and B are bound by memory bandwidth

- kernel C is bound by peak FLOP/s

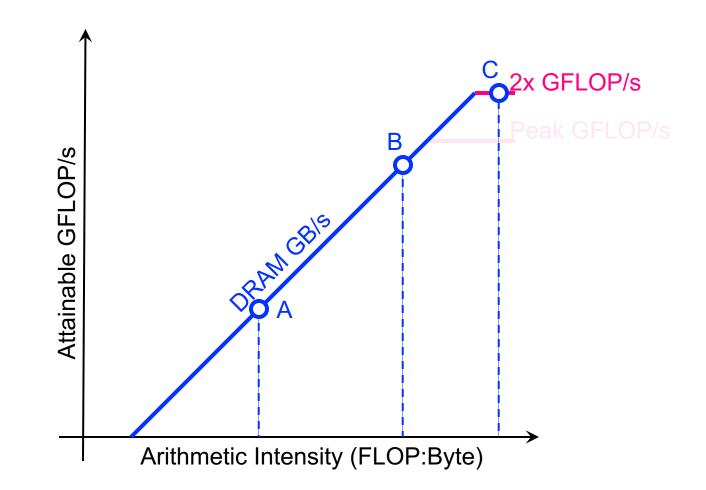

### **Scaling to Future GPUs**

- Imagine you run on a future GPU with twice the peak FLOPs...

- kernel C's performance could double

- **X** kernels A and B will be no faster

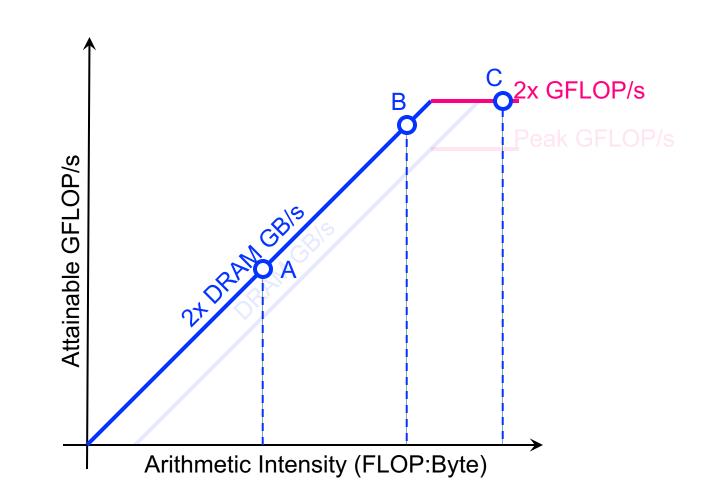

### **Scaling to Future GPUs**

- What if that future GPU also doubled its memory bandwidth...

- kernel A and B's performance could also double

Think back to our mix of loop nests where GFLOP/s alone wasn't useful...

• We can sort kernels by AI ...

- We can sort kernels by AI ...

- ... and compare performance relative to machine capabilities

- Kernels near the roofline are making good use of computational resources...

- kernels can have low performance (GFLOP/s), but make good use of a machine

- kernels can have high performance (GFLOP/s), but make poor use of a machine

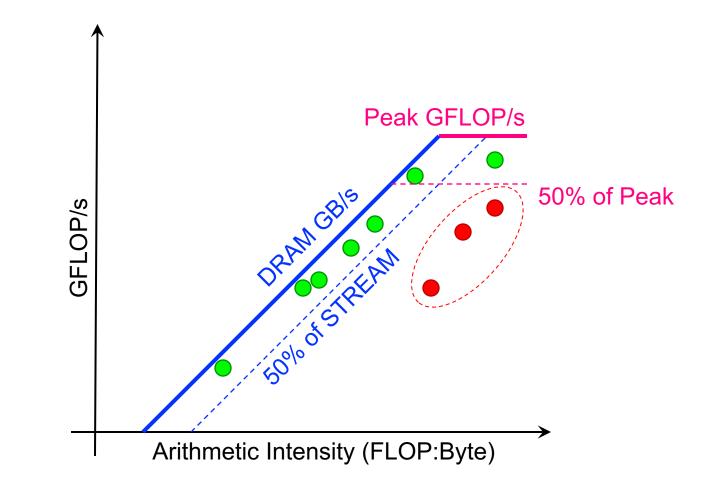

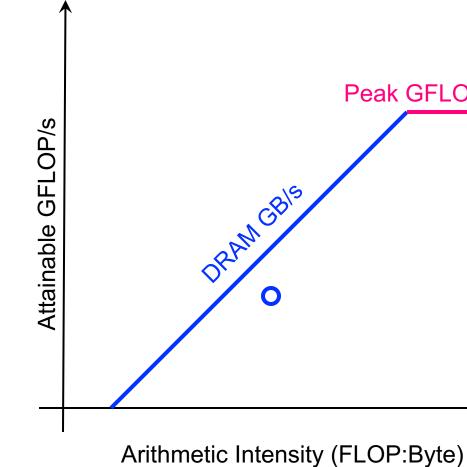

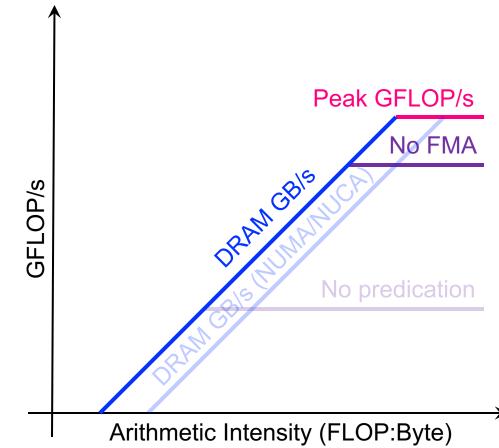

#### **Can Performance Be Below Roofline?**

- Analogous to asking whether one can always attain either...

- Peak Bandwidth  $\bigcirc$

- Peak GFLOP/s  $\bigcirc$

- Sure, there can be other performance bottlenecks...

- Cache bandwidth / locality Ο

- Lack of FMA / tensor instructions  $\bigcirc$

- Thread divergence / predication Ο

- Too many non-FP instructions Ο

Ο . . .

# Peak GFLOP/s

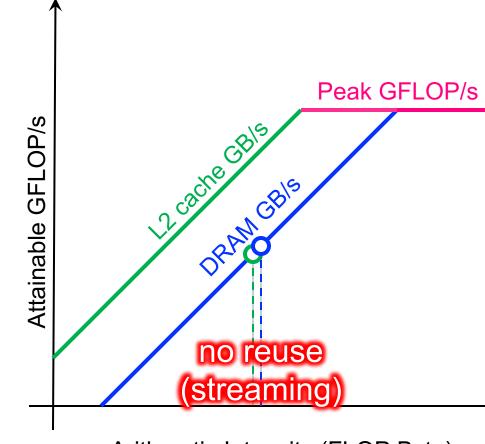

#### Cache Effects...

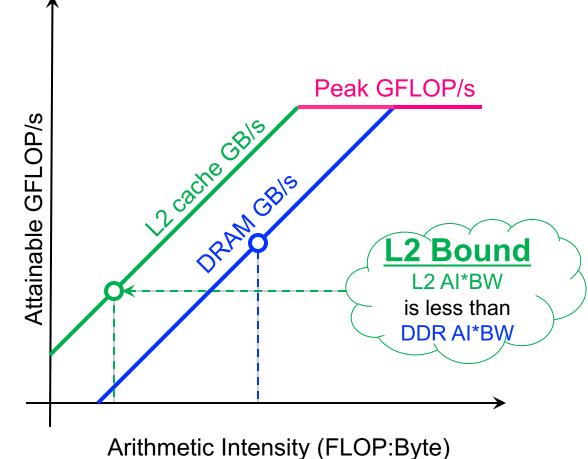

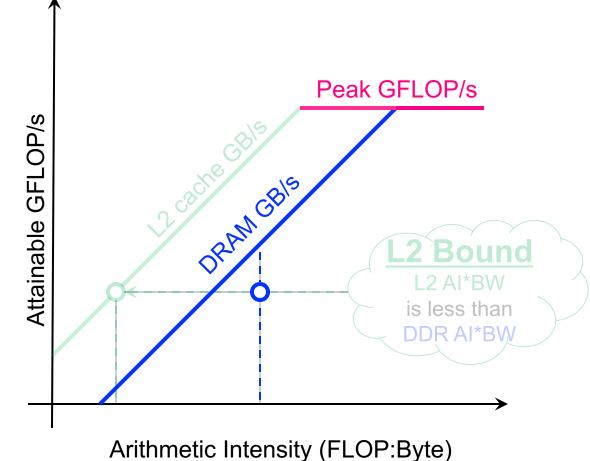

- Hierarchical Roofline Model

- Construct superposition of Rooflines...

- Measure AI and bandwidth for each  $\bigcirc$ level of memory/cache

- Loop nests will have multiple AI's and Ο multiple performance bounds...

- ... but performance is ultimately the minimum of these bounds.

#### Cache Effects...

- Hierarchical Roofline Model

- Construct superposition of Rooflines...

- Measure AI and bandwidth for each level of memory/cache

- Loop nests will have multiple AI's and Ο multiple performance bounds...

- ... but performance is ultimately the 0 minimum of these bounds.

- Extend to other memories...

- L1 / Shared

- System Ο

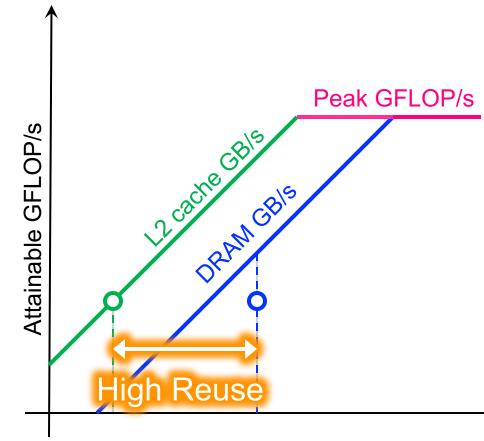

# Insights – Exploiting Caches

Widely separated Arithmetic Intensities indicate high reuse in the cache

Arithmetic Intensity (FLOP:Byte)

# Insights – Exploiting Caches

- Widely separated Arithmetic Intensities indicate high reuse in the cache

- Similar Arithmetic Intensities indicate effectively no cache reuse (== streaming)

- As one changes problem size, L2 and DRAM arithmetic intensities can behave very differently

Arithmetic Intensity (FLOP:Byte)

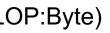

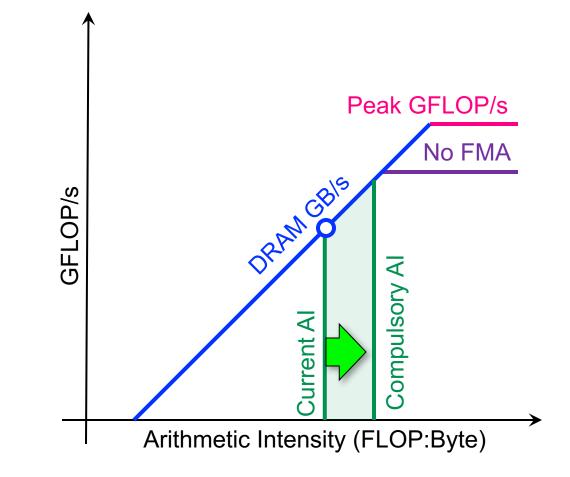

### Failure to Exploit CISC Instructions

- Death of Moore's Law is motivating a return of Complex Instruction Set Computing (CISC)

- Modern CPUs and GPUs are increasingly reliant on special (fused) instructions that perform multiple operations.

- FMA (Fused Multiply Add):  $z=a^{*}x+y$ ...*z*,*x*,*y* are vectors or scalars Ο

- 4FMA (quad FMA): z=A\*x+z ... A is a FP32 matrix; x,z are vectors

- HMMA (Tensor Core): Z=AB+C ...Z,A,B,C are FP16 matrices Ο

- Ο . . .

#### Performance is now a weighted average of Mul/Add, FMA, and HMMA operations.

### Failure to Exploit CISC Instructions

- Total lack of FMA reduces Volta performance by 2x...

- o creates ADD.f64 ceiling

- In reality, applications are a mix of FMA.f64, ADD.f64, and MUL.f64...

- Performance is a weighted average

- Produces a partial FMA ceiling that bounds kernel performance

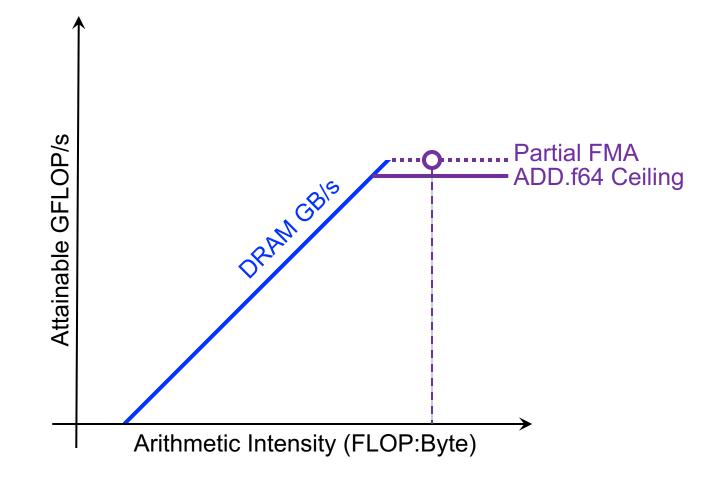

### Failure to Exploit CISC Instructions

- On Volta, Tensor cores provide 125 TFLOPs of FP16 performance (vs. 15 for FP32)

- However, kernels/apps will mix HMMA with FMA, MULs, ADDs, ...

- A few non-HMMA operations can quickly limit Tensor core performance

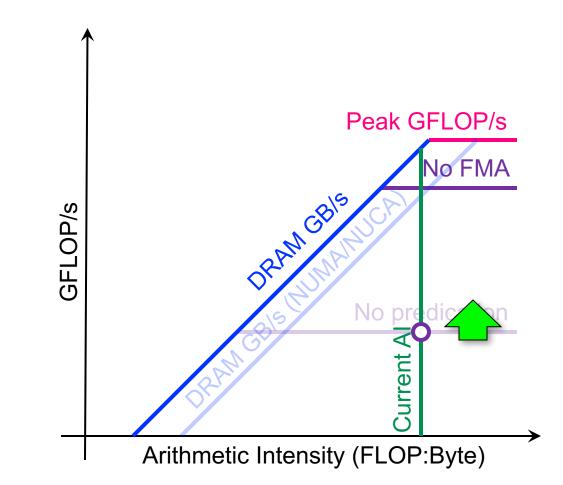

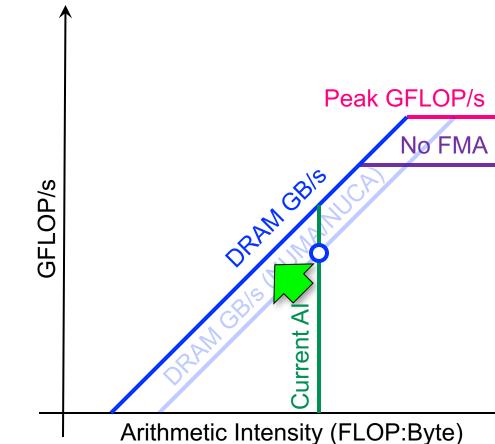

# **Using Roofline To Drive Optimization**

Broadly speaking, there are three approaches to improving performance:

- Broadly speaking, there are three approaches to improving performance:

- Maximize SM performance (e.g. minimize predication)

- Broadly speaking, there are three approaches to improving performance:

- Maximize SM performance (e.g. minimize predication)

- Maximize memory bandwidth (e.g. avoid pathological memory access patterns)

- Broadly speaking, there are three approaches to improving performance:

- Maximize SM performance (e.g. minimize predication)

- Maximize memory bandwidth (e.g. avoid pathological memory access patterns)

- Minimize data movement (i.e. exploit reuse)

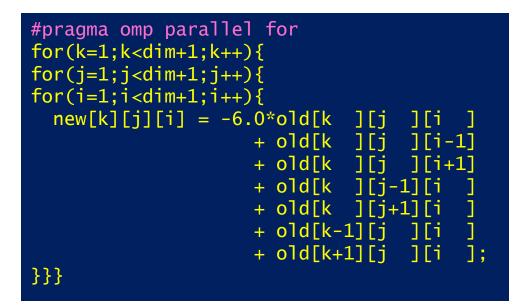

# **Estimating Arithmetic Intensity**

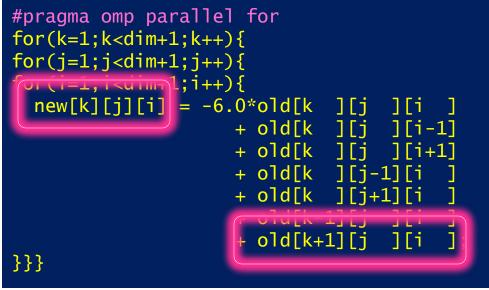

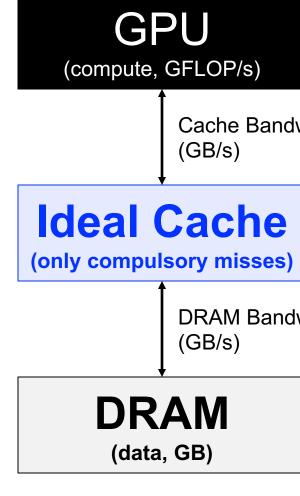

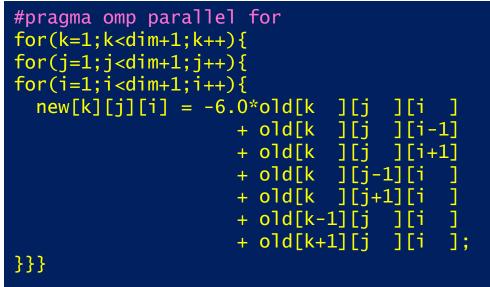

### **DRAM vs L1 Arithmetic Intensity**

- Consider a 7-point constant coefficient stencil...

- o 7 FLOPs

- 8 memory references (7 reads, 1 store) per point

- AI = 0.11 FLOPs per byte (L1)

**DRAM** (data, GB)

#### GPU (compute, GFLOP/s)

#### DRAM Bandwidth (GB/s)

#### **M** 3)

# **DRAM vs L1 Arithmetic Intensity**

- Consider a 7-point constant coefficient stencil...

- 7 FLOPs  $\bigcirc$

- 8 memory references (7 reads, 1 store) per point Ο

- Cache can filter all but 1 read and 1 write per point Ο

#### AI = 0.44 FLOPs per byte Ο

Cache Bandwidth

**DRAM Bandwidth**

# **DRAM vs L1 Arithmetic Intensity**

32

- Consider a 7-point constant coefficient stencil...

- o 7 FLOPs

- 8 memory references (7 reads, 1 store) per point

- Cache can filter all but 1 read and 1 write per point

- AI = 0.44 FLOPs per byte == memory bound

# Collecting Roofline Data with nvprof

#### **General Roofline Data Collection**

Most kernels are more complicated than the 7-point stencil...

#### **General Roofline Data Collection**

Most kernels are more complicated than the 7-point stencil...

How do we measure the total number of FLOPs? How do we measure the total number of bytes moved (read/write, L1/L2/HBM)? How do we measure the runtime for each kernel?

How do we know the peak bandwidth (L1/L2/HBM) and the peak FLOP/s for the architecture?

## **General Roofline Data Collection**

Most kernels are more complicated than the 7-point stencil...

How do we measure the total number of FLOPs? How do we measure the total number of bytes moved (read/write, L1/L2/HBM)? How do we measure the runtime for each kernel?

How do we know the peak bandwidth (L1/L2/HBM) and the peak FLOP/s for the architecture?

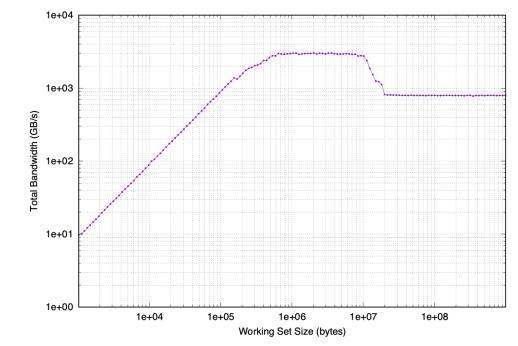

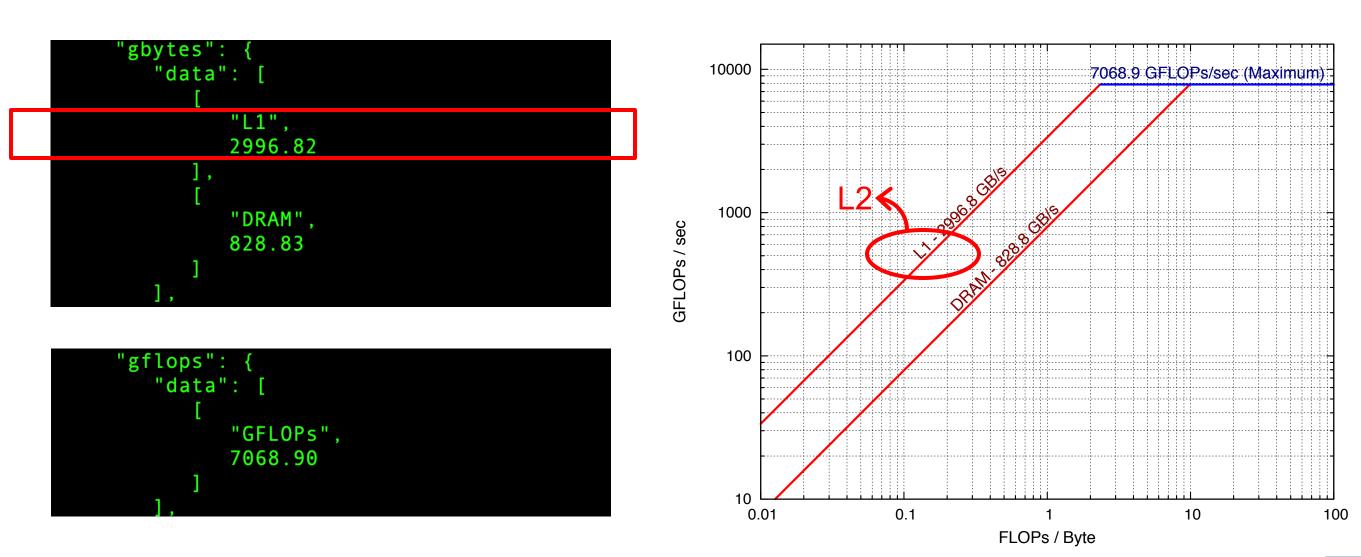

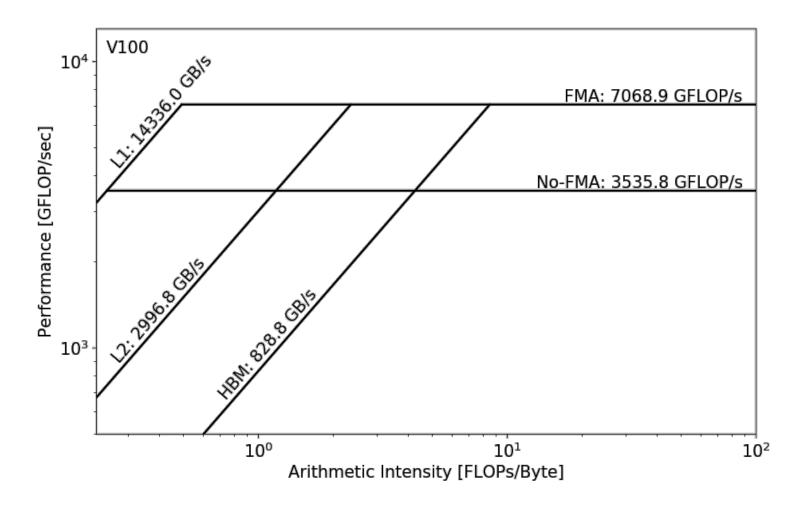

# Step 1. Collect Roofline Ceilings

- Empirical Roofline Toolkit (ERT)

- Different than the architecture specs, MORE REALISTIC

- Reflects actual execution environment (power constraints, etc)

- Sweeps through a range of configurations, and statistically stable

- Data elements per thread

- FLOPs per data element

- Threadblocks/threads

- Trails per dataset

- etc

## **STIC** raints, *etc)* **stically stable**

# **ERT Configuration**

| <ul> <li>Kernel.c</li> <li>actual compute</li> <li>customizable</li> </ul> | <ul> <li>Driver.c</li> <li>setup</li> <li>call kernels</li> <li>loop over parameters</li> </ul> |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| <ul> <li>config script</li> <li>set up ranges of parameters</li> </ul>     | job script<br>• submit the job and ru                                                           |

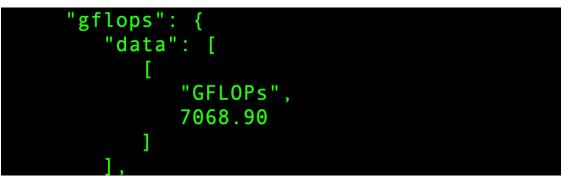

## 1000

roofline.ps

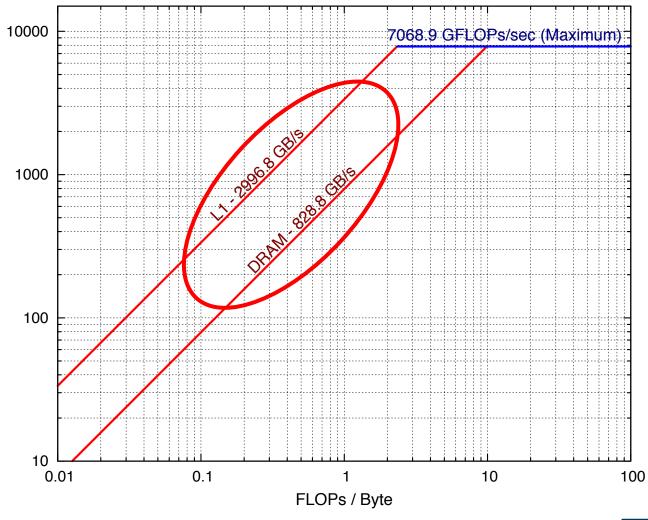

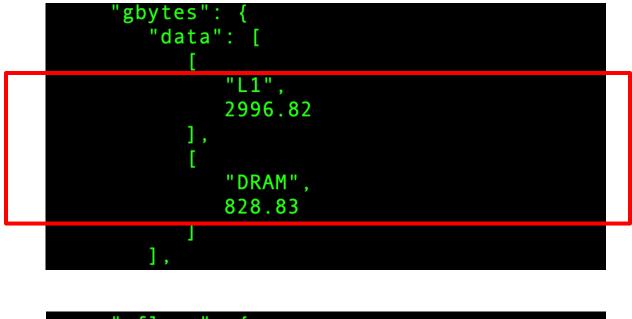

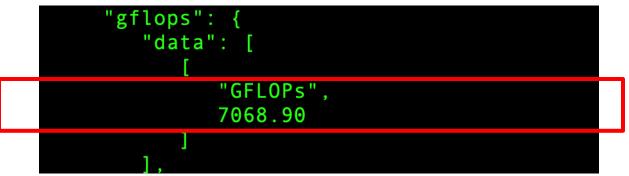

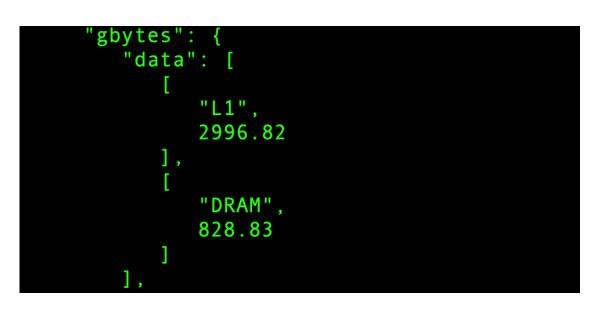

# **ERT Output**

## roofline.json

# **ERT Output**

roofline.json

roofline.ps

NVIDIA V100 -- Voltar at UOregon

# **ERT Output**

roofline.json

NVIDIA V100 -- Voltar at UOregon

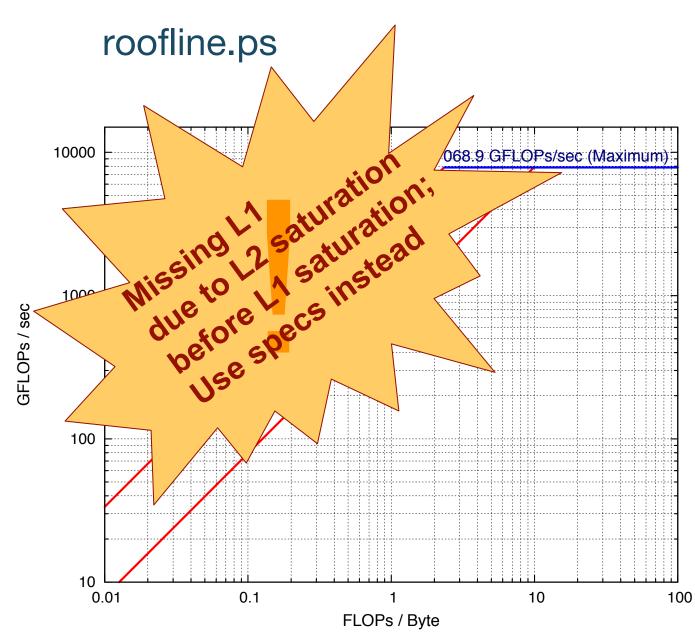

# **Discrepancy Empirical vs. Theoretical**

- Theoretical FP64 **compute** ceilings on V100:

- 80 SMs x 32 FP64 cores x 1.53 GHz x 2 = 7.83 TFLOP/s FMA:

- no FMA: 80 SMs x 32 FP64 cores x 1.53 GHz = 3.92 TFLOP/s

- Theoretical **memory** bandwidths on V100:

- HBM: 900 GB/s

- L2: ~4.1 TB/s

- L1: ~14 TB/s

- You may never achieve 7.8 TFLOP/s

- You may be closer to the ceiling than you think you are

## Theoretical FMA: 7833.6 GFLOP/s 10% Empirical FMA: 7068.9 GFLOP/s Theoretical No-FMA: 3916.8 GFLOP/s 10% Empirical No-FMA: 3535.8 GFLOP/s $10^{3}$ $10^{4}$

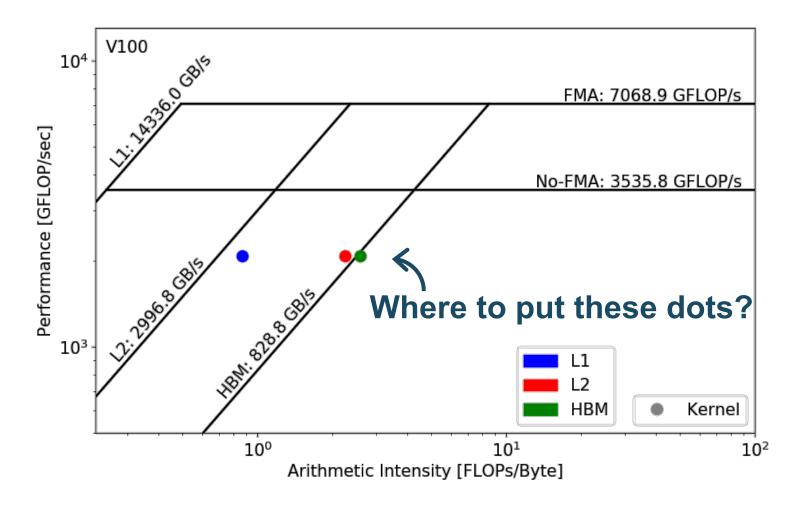

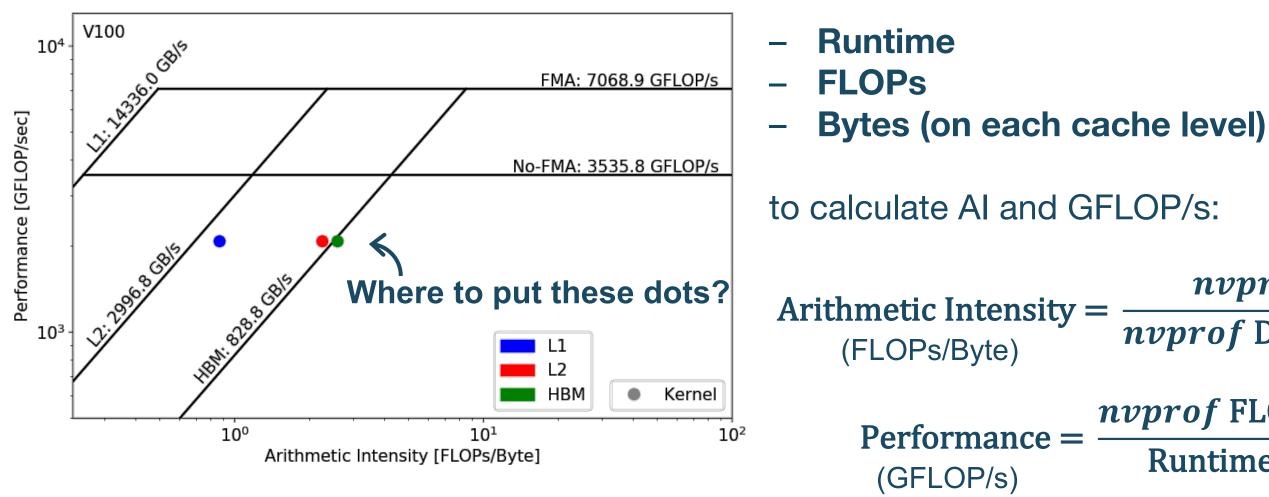

## **Step 2. Collect Application Performance**

## **Step 2. Collect Application Performance**

## **Step 2. Collect Application Performance**

## *nvprof* FLOPs *nvprof* Data Movement

## *nvprof* FLOPs **Runtime**

# **Collect Application Performance**

- **Runtime:**

- Time per invocation of a kernel

- nvprof --print-gpu-trace ./application

- Average time over multiple invocations

nvprof --print-gpu-summary ./application

- Same kernel with different input parameters are grouped separately

- FLOPs:

- Predication aware and complex-operation aware (such as divides)

- nvprof --kernels `kernel name' --metrics `flop count xx' ./application

- e.g. flop\_count\_{dp/dp\_add/dp\_mul/dp\_fma, sp\*, hp\*}

# **Collect Application Performance**

- Bytes for different cache levels in order to construct hierarchical Roofline:

- Bytes = (read transactions + write transactions) x transaction size

- nvprof --kernels `kernel name' --metrics `metric name'

./application

| Level              | Metrics                                                                                                                                                                            | Transaction<br>Size |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| First Level Cache* | <pre>gld_transactions, gst_transactions, atomic_transactions,<br/>local_load_transactions, local_store_transactions,<br/>shared_load_transactions, shared_store_transactions</pre> | 32B                 |

| Second Level Cache | <pre>12_read_transactions, 12_write_transactions</pre>                                                                                                                             | 32B                 |

| Device Memory      | dram_read_transactions, dram_write_transactions                                                                                                                                    | 32B                 |

| System Memory      | <pre>system_read_transactions, system_write_transactions</pre>                                                                                                                     | 32B                 |

Note: surface and texture transactions are ignored here for simplicity (HPC applications)

## **Example Output**

[cjyang@voltar source]\$ nvprof --kernels "1:7:smooth kernel:1" --metrics flop count dp --metrics gld transactions --metrics gst transactions -metrics 12 read transactions --metrics 12 write transactions --metrics dram read transactions --metrics dram write transactions --metrics sysmem read bytes --metrics sysmem write bytes ./hpgmg-fv-fp 5 8

Export to CSV: --csv -o nvprof.out

context : stream : kernel : invocation

| Invocations             | Metric Name                                                                                                                                                        | Metric Description                                              | Min      | Max      | Avg      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|----------|----------|

| Device "Tesla V100-PCIE | E-16GB (0)"                                                                                                                                                        |                                                                 |          |          | _        |

| Kernel: void smooth     | n_kernel <int=6, i<="" int="4," td=""><td><pre>int=8&gt;(level_type, int, int, double, double, int,</pre></td><td>double*,</td><td>double*)</td><td></td></int=6,> | <pre>int=8&gt;(level_type, int, int, double, double, int,</pre> | double*, | double*) |          |

| 1                       | flop_count_dp                                                                                                                                                      | Floating Point Operations(Double Precision)                     | 30277632 | 30277632 | 30277632 |

| 1                       | gld_transactions                                                                                                                                                   | Global Load Transactions                                        | 4280320  | 4280320  | 4280320  |

| 1                       | gst_transactions                                                                                                                                                   |                                                                 | 73728    | 73728    | 73728    |

| 1                       | <pre>l2_read_transactions</pre>                                                                                                                                    | L2 Read Transactions                                            | 890596   | 890596   | 890596   |

| 1                       | <pre>l2_write_transactions</pre>                                                                                                                                   | L2 Write Transactions                                           | 85927    | 85927    | 85927    |

| 1                       | dram_read_transactions                                                                                                                                             | Device Memory Read Transactions                                 | 702911   | 702911   | 702911   |

| 1                       | dram_write_transactions                                                                                                                                            | Device Memory Write Transactions                                | 151487   | 151487   | 151487   |

| 1                       | sysmem_read_bytes                                                                                                                                                  | System Memory Read Bytes                                        | Θ        | Θ        | Θ        |

| 1                       | sysmem_write_bytes                                                                                                                                                 | System Memory Write Bytes                                       | 160      | 160      | 160      |

|                         |                                                                                                                                                                    |                                                                 |          |          |          |

# **Step 3. Plot Roofline with Python**

- Calculate Arithmetic Intensity and GFLOP/s performance

- x coordinate: Arithmetic Intensity

- y coordinate: GFLOP/s performance

- Plot Roofline with Python Matplotlib

- Example scripts:

- https://github.com/cyanguwa/nersc-roofline/tree/master/Plotting

- Tweak as needed for more complex Rooflines

## *nvprof* FLOPs nvprof Data Movement

## **Plot Roofline with Python**

- Quick example: plot roofline.py data.txt

- Accepts space-delimited list for values

- Use quotes to separate names/labels

- **1. Collect Roofline ceilings**

- ERT: https://bitbucket.org/berkeleylab/cs-roofline-toolkit

- compute (FMA/no FMA) and bandwidth (DRAM, L2, ...)

- 2. Collect application performance

- nvprof: --metrics, --events, --print-gpu-trace

- FLOPs, bytes (DRAM, L2, ...), runtime

## **3. Plot Roofline with Python Matplotlib**

- arithmetic intensity, GFLOP/s performance, ceilings

- example scripts: https://github.com/cyanguwa/nersc-roofline

- **1. Collect Roofline ceilings**

- ERT: https://bitbucket.org/berkeleylab/cs-roofline-toolkit

- **compute** (FMA/no FMA) and **bandwidth** (DRAM, L2, ...)

- 2. Collect application performance

- nvprof: --metrics, --events, --print-gpu-trace

- FLOPs, bytes (DRAM, L2, ...), runtime

- 3. Plot Roofline with Python Matplotlib

- arithmetic intensity, GFLOP/s performance, ceilings

- example scripts: https://github.com/cyanguwa/nersc-roofline

- **1. Collect Roofline ceilings**

- ERT: https://bitbucket.org/berkeleylab/cs-roofline-toolkit

- **compute** (FMA/no FMA) and **bandwidth** (DRAM, L2, ...)

- 2. Collect application performance

- nvprof: --metrics, --events, --print-gpu-trace

- FLOPs, bytes (DRAM, L2, ...), runtime

- 3. Plot Roofline with Python Matplotlib

- arithmetic intensity, GFLOP/s performance, ceilings

- example scripts: https://github.com/cyanguwa/nersc-roofline

- **1. Collect Roofline ceilings**

- ERT: https://bitbucket.org/berkeleylab/cs-roofline-toolkit

- compute (FMA/no FMA) and bandwidth (DRAM, L2, …)

- 2. Collect application performance

- nvprof: --metrics, --events, --print-gpu-trace

- FLOPs, bytes (DRAM, L2, …), runtime

- 3. Plot Roofline with Python Matplotlib

- arithmetic intensity, GFLOP/s performance, ceilings

- example scripts: https://github.com/cyanguwa/nersc-roofline

## olkit 2, ...)

# **Roofline Analysis with Use Cases**

- GPP (General Plasmon Pole) kernel from BerkeleyGW (Material Science)

- https://github.com/cyanguwa/BerkeleyGW-GPP

- Medium problem size: 512 2 32768 20

- Tensor-contraction, abundant parallelism, large reductions

- Low FMA counts, divides, complex double data type, HBM data 1.5GB

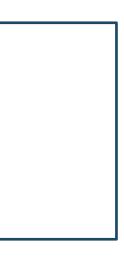

## **Pseudo Code**

| do band = 1, nbands | #blockIdx.x             |

|---------------------|-------------------------|

| do igp = 1, ngpown  | <pre>#blockIdx.y</pre>  |

| do ig = 1, ncouls   | <pre>#threadIdx.x</pre> |

| do iw = 1, nw       | #unrolled               |

| compute; reduct     | tions                   |

Three experiments:

| Vary <b>nw</b> from 1 to 6 | To study impact of varying Arithmetic Intensity on   |

|----------------------------|------------------------------------------------------|

| Compile w/wo FMA           | To study impact of instruction mix on performance of |

| Stride <b>ig</b> loop      | To study impact of suboptimal memory coalescing      |

- Note that **nvprof** has already taken care of

- Appropriate counting of FLOPs for complex instructions

- div, exp, log and sin/cos should be counted as multiple FLOPs rather than 1 •

- Appropriate counting of FLOPs for predicated-out threads

- FLOPs are only counted on non-predicated threads •

## performance on performance on performance

- Highly parameterizable

- 1. Varying **nw** from 1 to 6 to increase arithmetic intensity

- FLOPs increases, but data movement stays (at least for HBM)

## Pseudo Code

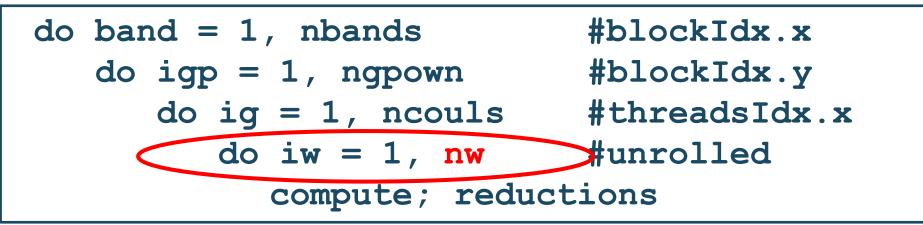

- 2. Compiling with and without FMA

- -fmad=true/false

- Highly parameterizable

- 3. Striding ig loop to analyze impact of suboptimal memory coalescing

- Split ig loop to two loops and place the 'blocking' loop outside

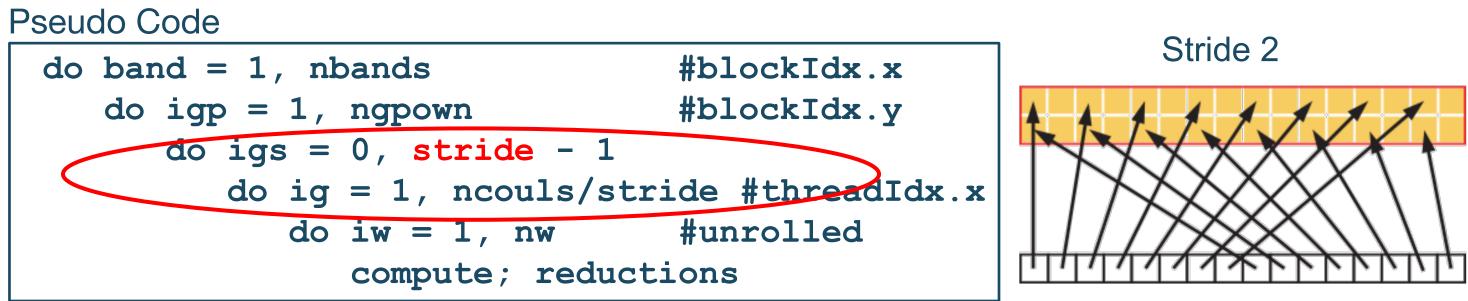

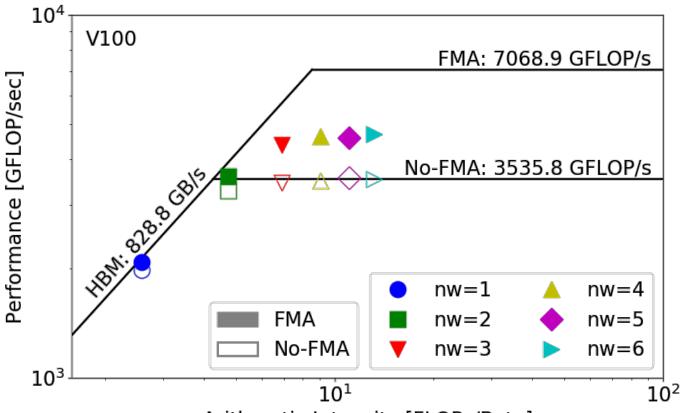

- **Experiments 1**: study the impact of varying AI on performance

- HBM Roofline, i.e. bytes are HBM bytes

- Al increases as **nw** grows

- GPP moves from a bandwidth bound region to a compute bound region

Roofline captures the change in Al

- **Experiments 1 & 2:** study the impact of instruction mix on performance

- HBM Roofline, i.e. bytes are HBM bytes

- No-FMA performance converges to the no-FMA ceiling, but FMA performance is still far from the FMA ceiling

- Not reaching FMA ceiling due to lack of FMA instructions

- Roofline captures effects of instruction mix

## Arithmetic Intensity [FLOPs/Byte]

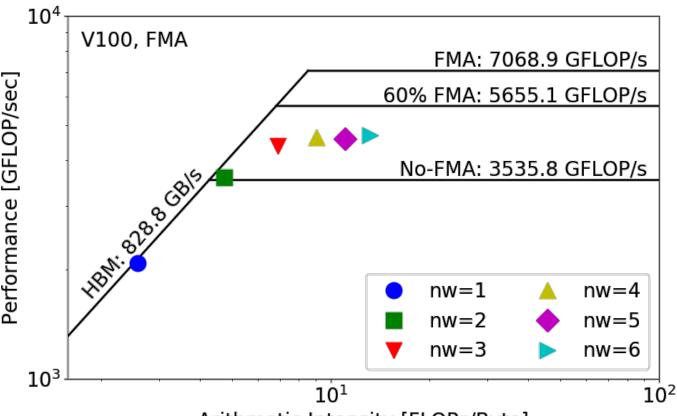

- **Experiments 1 & 2:** study the impact of instruction mix on performance

- At nw=6, GPP has  $\alpha = \frac{\text{FMA FP64 instr.}}{\text{FMA FP64 instr.} + \text{non} \text{FMA FP64 instr.}} = 60\%$  of FMA instructions

- $\beta, \zeta_{n}$ , pected performance is  $\beta = \frac{\alpha \times 2 + (1 \alpha)}{2} = 80\% \text{ of compute peak.}$ -6 GPP is only achieving 66%. $\sum be taking equal by the taking equa by the taking equal by t$ up the instruction issue/execution pipeline

- Partial Roofline can show you the headroom

## Arithmetic Intensity [FLOPs/Byte]

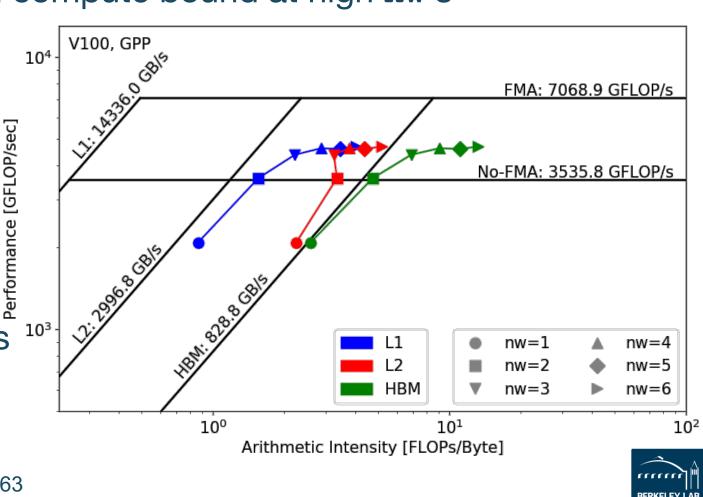

- **Experiments 1 & 2:** What else is going on?

- Hierarchical Roofline, i.e. bytes are HBM, L2 and unified L1 cache bytes

- GPP is HBM bound at low **nw**'s and compute bound at high **nw**'s

- FLOPs < nw

- HBM bytes: constant

- L2 bytes: increasing at  $\alpha > 1$

- L1 bytes: constant

- Spike in L2 curve at **nw**=2, 3

- Hierarchical Roofline captures more details about cache locality

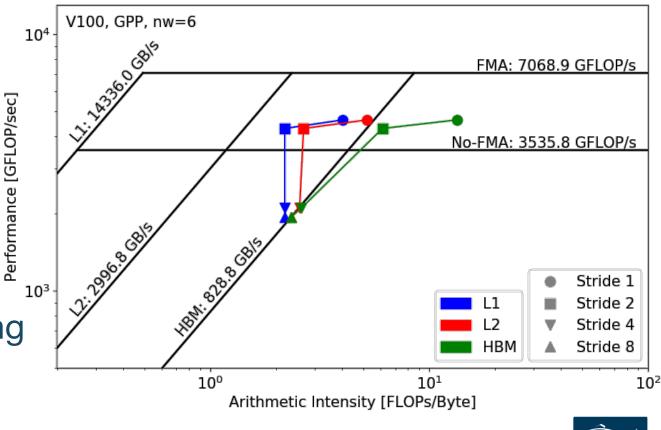

- **Experiment 3:** study the effects of suboptimal memory coalescing **nw**=6

- Hierarchical Roofline, i.e. bytes are HBM, L2 and unified L1 cache bytes

- L1/L2 bytes doubles from stride 1 to 2, but stays almost constant afterwards

- at **nw**=6, GPP moves from compute bound to bandwidth bound

- Eventually all dots converge to HBM

- Roofline captures effects of memory coalescing

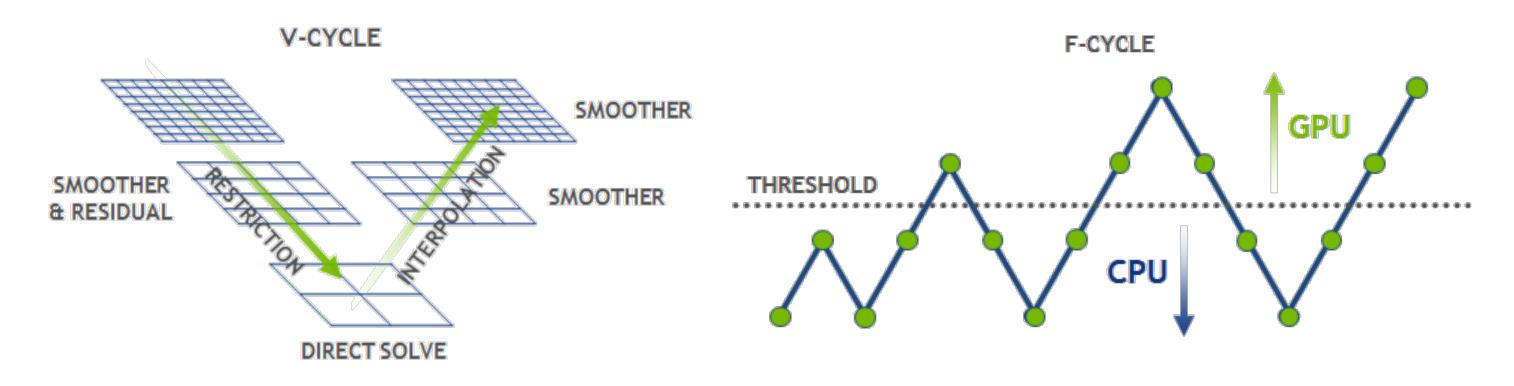

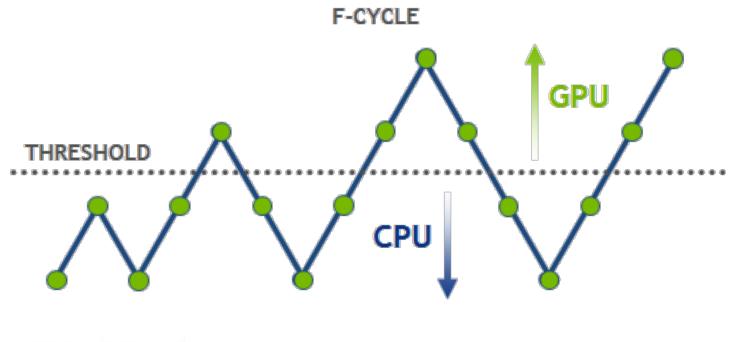

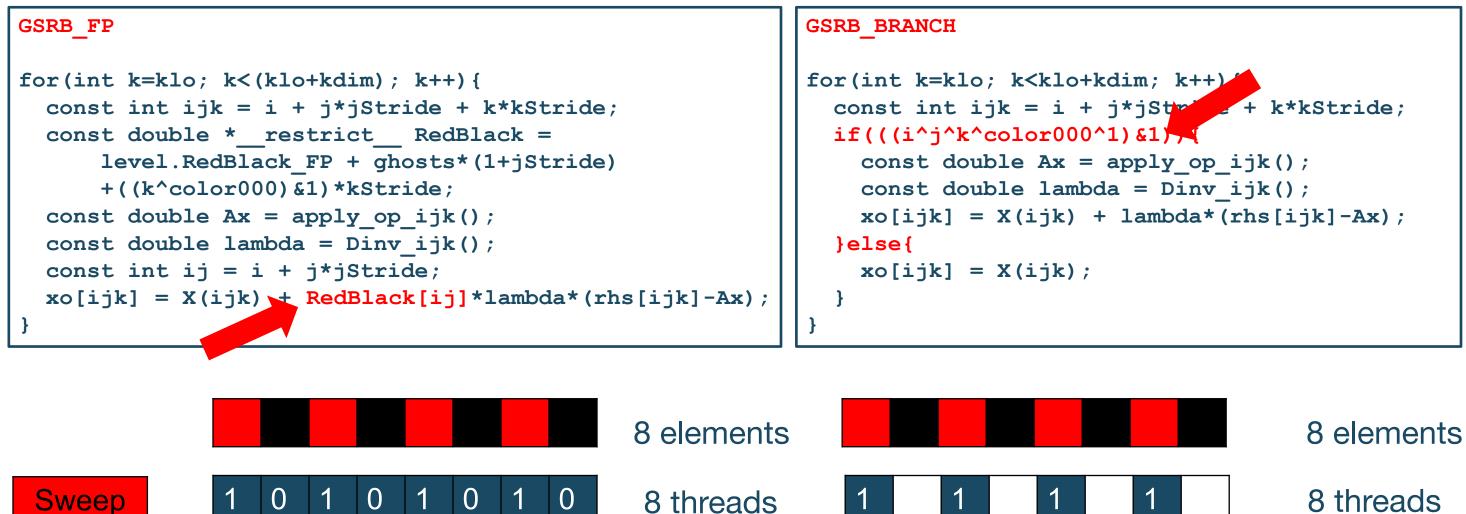

- HPGMG (High-performance Geometric Multigrid) from Adaptive Mesh Refinement codes

- https://bitbucket.org/nsakharnykh/hpgmg-cuda

- Stencil code, F-cycles and V-cycles, GSRB smoother kernel (Gauss-Seidel Red-Black)

HPGMG. https://devblogs.nvidia.com/high-performance-geometric-multi-grid-gpu-acceleration/

- Hybrid GPU and CPU code

- Example: hpgmg-fv 7 8

- 128<sup>3</sup> box x 8, Level 5-8 run on GPU, Level 1-4 on CPU

- Three versions of GSRB kernel

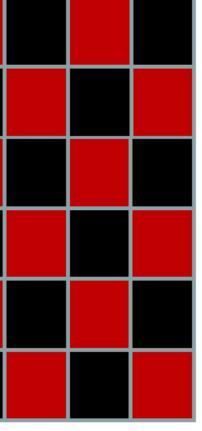

- GSRB\_FP, GSRB\_BRANCH, GSRB\_STRIDE2

## GSRB FP

```

for(int k=klo; k<(klo+kdim); k++){

const int ijk = i + j*jStride + k*kStride;

const double *_restrict__ RedBlack =

level.RedBlack_FP + ghosts*(1+jStride)

+((k^color000)&1)*kStride;

const double Ax = apply_op_ijk();

const double lambda = Dinv_ijk();

const int ij = i + j*jStride;

xo[ijk] = X(ijk) + RedBlack[ij]*lambda*(rhs[ijk]-Ax);

}</pre>

```

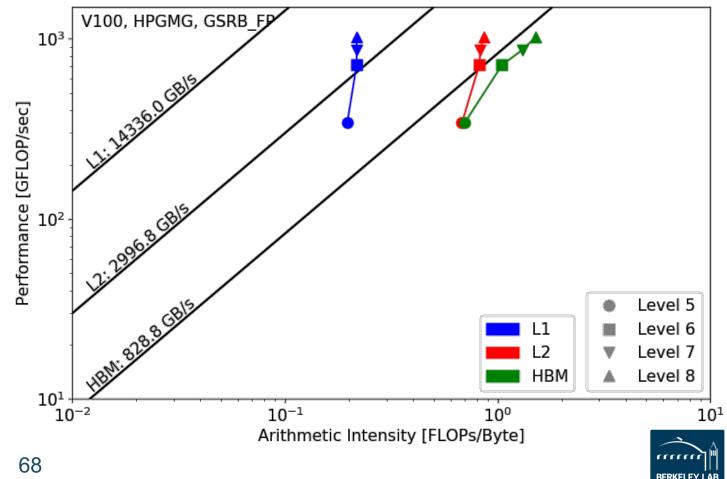

## **GSRB\_FP**

- Hierarchical Roofline, i.e. bytes are HBM, L2 and unified L1 cache bytes

- Highly bandwidth bound, inherent to stencil codes

- From Level 5 to Level 8:

- Al slightly increases due to

- better Surface: Volume ratio

- More HBM bound as more data is read in

Roofline captures computational characteristics of the algorithm

Office of Science

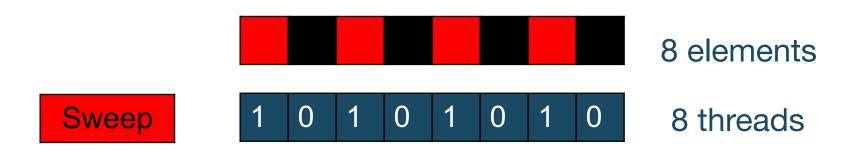

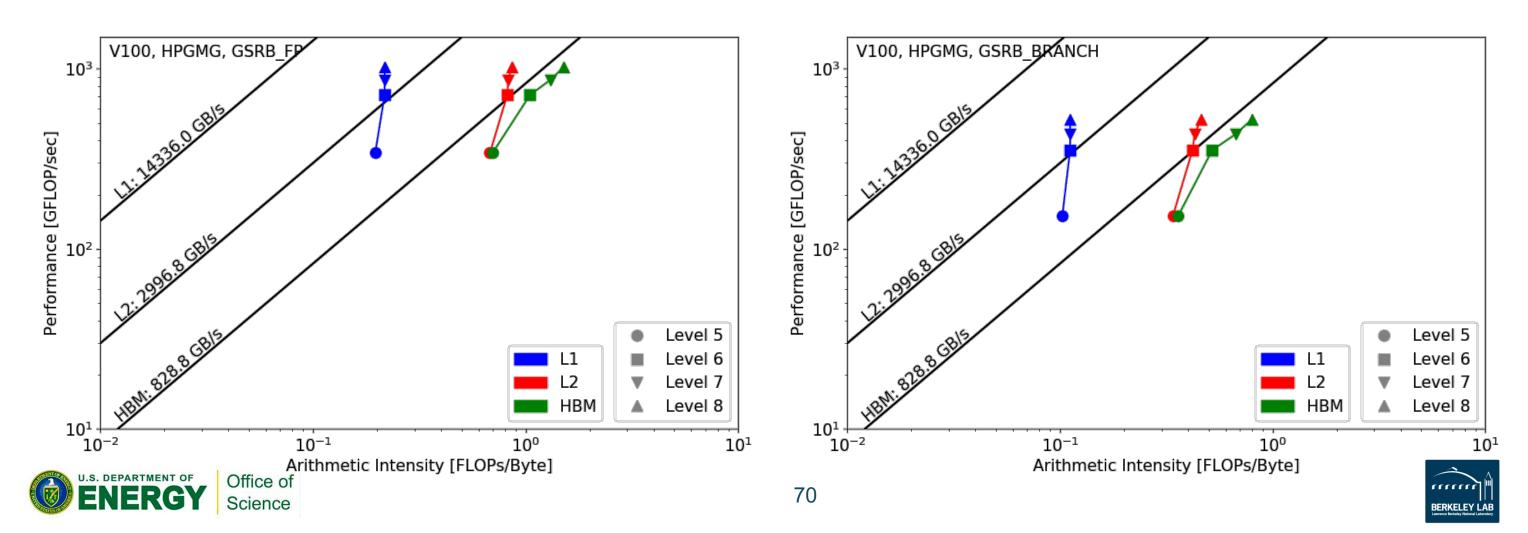

GSRB BRANCH has half the FLOPs as GSRB FP but the same HBM/L1/L2 bytes

## 8 threads

## **GSRB\_FP vs. GSRB\_BRANCH**

- FLOPs halves, bytes doesn't change, thus AI halves and GFLOP/s halves

- Runtime is comparable even though GFLOP/s has halved

- Same number of threads occupied, only with half predicated in GSRB\_BRANCH

```

GSRB STRIDE2

for(int k=klo; k<klo+kdim; k++) {</pre>

i = ilo +!((ilo^{\dagger}k^{color000}) \& 1) + threadIdx.x^{2};

if(i < ilo+idim) {</pre>

const int ijk = i + j _____stride + k*kStride;

xo[ijk] = X(ijk);

i = ilo + ((ilo^j^k^color000)&1) + threadIdx.x*2;

if(i < ilo+idim) {</pre>

const int ijk = i + j*jStride + k*kStride;

const double Ax = apply_op_ijk();

const double lambda = Dinv ijk();

xo[ijk] = X(ijk) + lambda*(rhs[ijk]-Ax);

```

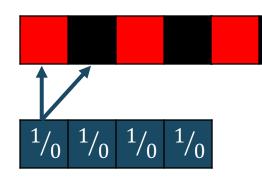

GSRB\_STRIDE2 should have the same FLOPs as GSRB\_BRANCH, but same bytes? More writes than GSRB\_BRANCH?

## 8 elements

## 4 threads

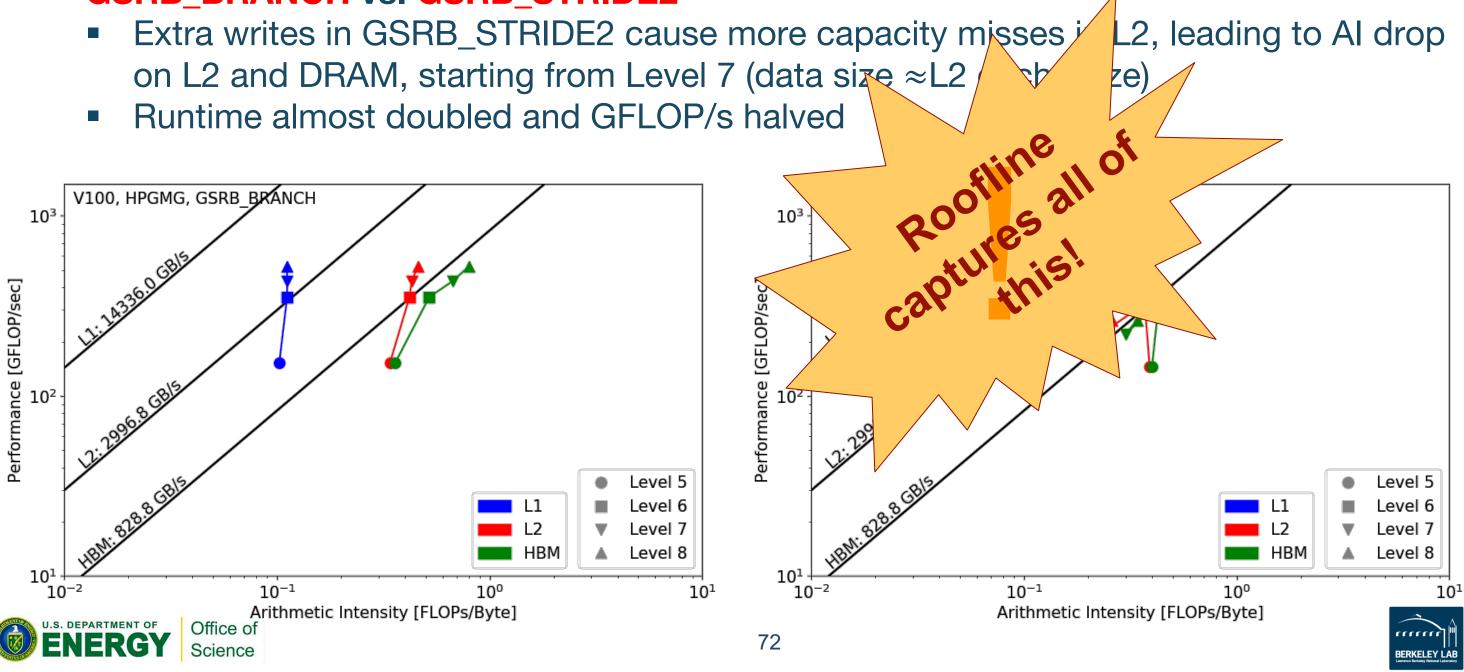

## **GSRB\_BRANCH vs. GSRB\_STRIDE2**

- Extra writes in GSRB\_STRIDE2 cause more capacity misses on L2 and DRAM, starting from Level 7 (data size  $\approx$ L2

- Runtime almost doubled and GFLOP/s halved

## Conclusions

- Roofline can gracefully capture various aspects of application performance and architecture characteristics such as arithmetic intensity, instruction mix, memory coalescing and thread predication.

- The proposed methodology is effective in collecting machine characteristics and application data on NVIDIA GPUs to construct **hierarc**

- The Roofline model provides insights that profile

- identify the most immediate bottleneck

- prioritize optimization efforts

- tell you when you can stop

## Reference

- S. Williams, A. Waterman and D. Patterson, "Roofline: An insightful visual performance model for multicore architectures," Communications of the ACM, vol. 52, no. 4, pp. 65–76, 2009

- Empirical Roofline Toolkit (ERT): <u>https://bitbucket.org/berkeleylab/cs-roofline-toolkit</u>

- Example scripts for plotting Roofline: <u>https://github.com/cyanguwa/nersc-roofline</u>

- General Plasmon Pole kernel: https://github.com/cyanguwa/BerkeleyGW-GPP

- HPGMG-CUDA kernel: https://bitbucket.org/nsakharnykh/hpgmg-cuda

## Acknowledgement

- This material is based upon work supported by the Advanced Scientific Computing Research Program in the U.S. Department of Energy, Office of Science, under Award Number DE-AC02-05CH11231.

- This material is based upon work supported by the DOE RAPIDS SciDAC Institute.

- This research used resources of the National Energy Research Scientific Computing Center (NERSC), which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02-05CH11231.

## **Thank You!**