## Optimizing for Intel Xeon Phi Knights Landing

Steven Warren

#### Legal Disclaimer

Information in this document is provided in connection with Cray Inc. products. No license, express or implied, to any intellectual property rights is granted by this document.

Cray Inc. may make changes to specifications and product descriptions at any time, without notice.

All products, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

Cray hardware and software products may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Cray uses codenames internally to identify products that are in development and not yet publicly announced for release. Customers and other third parties are not authorized by Cray Inc. to use codenames in advertising, promotion or marketing and any use of Cray Inc. internal codenames is at the sole risk of the user.

Performance tests and ratings are measured using specific systems and/or components and reflect the approximate performance of Cray Inc. products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance.

The following are trademarks of Cray Inc. and are registered in the United States and other countries: CRAY and design, SONEXION, URIKA and YARCDATA. The following are trademarks of Cray Inc.: CHAPEL, CLUSTER CONNECT, CLUSTERSTOR, CRAYDOC, CRAYPAT, CRAYPORT, DATAWARP, ECOPHLEX, LIBSCI, NODEKARE, REVEAL. The following system family marks, and associated model number marks, are trademarks of Cray Inc.: CS, CX, XC, XE, XK, XMT and XT. The registered trademark LINUX is used pursuant to a sublicense from LMI, the exclusive licensee of Linus Torvalds, owner of the mark on a worldwide basis. Other trademarks used on this website are the property of their respective owners.

#### Outline

- Make KNL run my code faster!

- Vectorization

- Cache blocking

- --exclusive

#### Optimizing for Intel Xeon Phi Knights Landing

- Many KNL-specific optimizations involve MCDRAM in "Flat" mode

- Since Cori uses "cache" mode, these optimizations generally do not apply

- If application can strong scale efficiently, can use enough nodes such that the memory footprint/node is less than 16 GB and fit into MCDRAM

- KNL is an x86 processor, thus many of the things you would do for any x86 processor will apply

- i.e., work done to improve KNL performance will generally improve performance on other modern processors as well

#### KNL strengths and weaknesses

- Strengths

- MCDRAM memory bandwidth

- Effectively a large L3 in "cache" mode (no dedicated L3 on KNL)

- Larger L2 per core (1 MB / 2-core tile)

- AVX512 vectors

- Allows more operations per cycle than previous generations of processors

- Weaknesses

- Clock GHz

- Affects scalar operations

- Optimization strategy

- Vectorize and/or cache block important kernels

But first, a note about affinity...

#### **Process / Thread / Memory Affinity**

- Correct process, thread and memory affinity is the basis for getting optimal performance on KNL. It is also essential for guiding further performance optimizations.

- Process Affinity: bind MPI tasks to CPUs

- Thread Affinity: bind threads to CPUs allocated to its MPI process

- Memory Affinity: allocate memory from specific NUMA domains

- Our goal is to promote OpenMP standard settings for portability. For example, OMP\_PROC\_BIND and OMP\_PLACES are preferred to Intel specific KMP\_AFFINITY and KMP\_PLACE\_THREADS settings.

The following NERSC slides stolen from Helen. Thanks Helen!

#### xthi.c

- XTHI is a <u>very</u> useful application that will tell you whether or not you are getting the expected placement behavior.

- <a href="https://github.com/olcf/XC30-Training/blob/master/affinity/Xthi.c">https://github.com/olcf/XC30-Training/blob/master/affinity/Xthi.c</a>

- Different compilers and MPI stacks have different affinity rules

- i.e., what works for Intel likely will not work for Cray or GNU

- Replace the call to your application binary to the xthi binary in your srun line to check affinity.

- Can do this at any scale, but it's best to change the number of PEs to use a single node to avoid confusion of the output.

#### "numactl -H" displays NUMA info

#### 68-core Quad Cache node:

NUMA Domain 0: all 68 cores (272 logic cores)

yunhe@cori01:> salloc -N 1 --qos=interactive -C knl,quad,cache -t 30:00

salloc: Granted job allocation 5291739

yunhe@nid02305:> numactl -H

available: 1 nodes (0)

node 0 cpus: 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223 224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239 240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255 256 257 258 259 260 261 262 263 264 265 266 267 268 269 270 271

node 0 size: 96762 MB node 0 free: 93067 MB

node distances:

node 0 0: 10

- The quad, cache mode has only 1 NUMA node with all CPUs on the NUMA node 0 (DDR memory)

- The MCDRAM is hidden from the numactl -H command (it is a cache).

#### Can We Just Do a Naïve Srun?

### Example: 16 MPI tasks x 8 OpenMP threads per task on a single 68-core KNL quad, cache node:

```

% export OMP_NUM_THREADS=8

% export OMP_PROC_BIND=spread

(other choice are "close","master","true","false")

% export OMP_PLACES=threads

ways to specify explicit lists, etc.)

```

#### % srun -n 16 ./xthi |sort -k4n,6n

```

Hello from rank 0, thread 0, on nid02304. (core affinity = 0)

Hello from rank 0, thread 1, on nid02304. (core affinity = 144)

Hello from rank 0, thread 2, on nid02304. (core affinity = 17)

Hello from rank 0, thread 3, on nid02304. (core affinity = 161)

Hello from rank 0, thread 4, on nid02304. (core affinity = 34)

Hello from rank 0, thread 5, on nid02304. (core affinity = 178)

Hello from rank 0, thread 6, on nid02304. (core affinity = 51)

Hello from rank 0, thread 7, on nid02304. (core affinity = 195)

Hello from rank 1, thread 0, on nid02304. (core affinity = 0)

Hello from rank 1, thread 1, on nid02304. (core affinity = 144)

```

#### It is a mess!

### Importance of -c and --cpu\_bind Options Options

- The reason: 68 is not divisible by #MPI tasks!

- Each MPI task is getting 68x4/#MPI tasks of logical cores as the domain size

- MPI tasks are crossing tile boundaries

- Set number of logical cores per MPI task (-c) manually by wasting extra 4 cores on purpose: 256/#MPI\_tasks\_per\_node.

- Meaning to use 64 cores only on the 68-core KNL node, and spread the logical cores allocated to each MPI task evenly among these 64 cores.

- Now it looks good!

- % srun -n 16 -c 16 --cpu\_bind=cores ./xthi

Hello from rank 0, thread 0, on nid09244. (core affinity = 0)

Hello from rank 0, thread 1, on nid09244. (core affinity = 136)

Hello from rank 0, thread 2, on nid09244. (core affinity = 1)

Hello from rank 0, thread 3, on nid09244. (core affinity = 137)

#### **Now It Looks Good!**

#### Process/thread affinity are good! (Marked first 6 and last MPI tasks only)

| 0   | 8   | 2                                 | 3   | 4   | 5   | 6   | 7   |     |     | 10  | 11  | 12  | 13  | 14  | 15  | 26  | 17  |

|-----|-----|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 68  | 69  | 70                                | 71  | 72  | 73  | 74  | 75  | 76  | 77  | 78  | 79  | 80  | 81  | 82  | 83  | 84  | 85  |

| 136 | 137 | 138                               | 139 | 140 | 141 | 142 | 143 | 144 | 145 | 146 | 147 | 148 | 149 | 150 | 151 | 152 | 153 |

| 204 |     |                                   |     |     |     | -   |     |     |     |     |     |     |     |     |     | 220 | 221 |

| 18  | 19  | 20                                | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  |

| 86  |     |                                   |     |     |     |     |     |     |     |     |     |     |     |     |     | 102 | 103 |

| 154 | 155 | 156                               | 157 | 158 | 159 | 160 | 161 |     |     |     |     |     |     |     |     | 170 | 171 |

| 222 |     |                                   |     |     |     |     |     |     |     |     |     |     |     |     |     | 238 | 239 |

| 36  | 37  | 38                                | 39  | 40  | 41  | 42  | 43  | 44  | 45  | 46  | 47  | 48  | 49  | 50  | 51  |     |     |

| 104 |     |                                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 172 |     | And so on for other MPI tasks and |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 240 |     | threads                           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 52  | 53  | 54                                | 55  | 56  | 57  | 58  | 59  | 60  | 61  | 62  | 63  | 64  | 65  | 66  | 67  |     |     |

| 120 |     |                                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 188 |     |                                   |     |     |     |     |     | 196 | 197 | 198 | 199 |     |     |     |     |     |     |

| 256 |     |                                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

MPI rank 15

# Essential Runtime Settings for Process/Thread Affinity

- Use srun -c and --cpu\_bind flags to bind tasks to CPUs

- -c <n> (or --cpus-per-task=n) allocates (reserves) n CPUs per task (process). It helps to evenly spread MPI tasks, can use up to n OpenMP threads per MPI task.

- Use --cpu\_bind=cores (no hyperthreads) or --cpu\_bind=threads (if hyperthreads are used)

- Use OpenMP envs: OMP\_PROC\_BIND, OMP\_PLACES to fine pin each thread to a subset of CPUs allocated to the host task

- Different compilers may have different implementations

- The following provide compatible thread affinity among Intel, GNU and Cray compilers:

- OMP\_PROC\_BIND=true # Specifying threads may not be moved between CPUs OMP\_PLACES=threads # Specifying a thread should be placed on a single CPU

- Verify with XTHI before running your code!

### But second... Dynamic vs Static linking on KNL

#### Dynamic vs Static Linking for Qbox on KNL

Lines 248 – 249 in qb.C require glibc, which is a collection of dynamic libraries in many current operating systems

```

if (getlogin() != 0)cout << "<user> " << getlogin() << " </user>" << endl;</li>

```

Performance can be greatly increased on KNL for statically linked executables.

#### Options to link statically

Can statically link in Cray Libsci libraries (executable remains dynamic) to alleviate some of the performance loss by setting:

```

LIBS = -WI,-Bstatic -lsci_cray_mpi_mp -lsci_cray_mp \

-lfftw3f_mpi -lfftw3f_omp -lfftw3f -lfftw3_mpi \

-lfftw3_omp -lfftw3 -WI,-Bdynamic

```

- Or compile fully static but add extra compile flags to qb.C:

- '-Dmain=stealthy(){return 0;} char\* stealth(){return getenv("USER");} int main' -Dgetlogin=stealth

Or one could simply modify the code in qb.C to use getenv() instead of getlogin() and compile fully static.

#### Dynamic vs Static Linking for Qbox on KNL

For a 256 node, 880 atom Qbox run using 32 MPI ranks/node and 2 OpenMP threads/rank with nrowmax set to 256 yields the following results:

| Link type              | Dynamic<br>Linking | Static<br>Linking | Dynamic Linking with Statically Linked Cray Libsci libraries |

|------------------------|--------------------|-------------------|--------------------------------------------------------------|

| max time<br>(run time) | 330 s              | 198 s             | 215 s                                                        |

# Example Analysis and Optimizations:

Vectorization

#### What is vectorization?

Vectorization is the practice of converting an algorithm to work on a set of values simultaneously instead of a single value one-by-one.

#### What prevents vectorization?

- Complexity in loops which the compiler can not interpret

- Indirect memory accesses

- Logical statements

- Recurrences on variables

#### How To Know If Your Loops Are Vectorizing

- CCE can provide "listing" files with compilation which will give an easily interpreted and detailed description of every line in your source

- -hlist=a

- Intel and GNU compiler provide similar capabilities.

- Use the listing file to determine if your changes allow the compiler to apply better optimizations

- You do NOT need to execute the code to check if the compiler applies optimizations

| 응응응 | Loopmark Le              | g e n d %%%                      |

|-----|--------------------------|----------------------------------|

|     | Primary Loop Type        | Modifiers                        |

|     |                          |                                  |

|     | A - Pattern matched      | a - atomic memory operation      |

|     |                          | b - blocked                      |

|     | C - Collapsed            | c - conditional and/or computed  |

|     | D - Deleted              |                                  |

|     | E - Cloned               |                                  |

|     | F - Flat - No calls      | f - fused                        |

|     | G - Accelerated          | g - partitioned                  |

|     | I - Inlined              | i - interchanged                 |

|     | M - Multithreaded        | m - partitioned                  |

|     |                          | n - non-blocking remote transfer |

|     |                          | p - partial                      |

|     | R - Rerolling            | r - unrolled                     |

|     |                          | s - shortloop                    |

|     | V - Vectorized           | w - unwound                      |

|     | + - More messages listed | at end of listing                |

|     |                          |                                  |

#### Example Loop

```

1 \ 2 \qquad PF = 0.0

67.

68. + 1 2 3--< DO 44030 I = 2, N

69. 1 2 3

AV = B(I) * RV

70. 1 2 3

PB = PF

71. 1 2 3

PF = C(I)

IF ((D(I) + D(I+1)) .LT. 0.) PF = -C(I+1)

72. 1 2 3

73. 1 2 3 AA = E(I) - E(I-1) + F(I) - F(I-1)

1 + G(I) + G(I-1) - H(I) - H(I-1)

74. 1 2 3

75. 1 2 3

BB = R(I) + S(I-1) + T(I) + T(I-1)

76. 1 2 3 1 -U(I) - U(I-1) + V(I) + V(I-1)

77. 1 2 3 2

- W(I) + W(I-1) - X(I) + X(I-1)

78. 1 2 3

A(I) = AV * (AA + BB + PF - PB + Y(I) - Z(I)) + A(I)

79. 1 2 3--> 44030 CONTINUE

ftn-6254 ftn: VECTOR LP44030, File = lp44030.f, Line = 68

A loop starting at line 68 was not vectorized because a recurrence was found on "pf"

at line 71.

```

- There is a recurrence on the scalar 'PF'

- Use the 'explain' tool to learn more about what a recurrence is

- > explain ftn-6254

### Example

#### What's Preventing Vectorization?

Let's do a vector dependency analysis assuming VL=2

Compiler will not promote PF to a 3 element vector

$$PB\begin{pmatrix}2\\3\end{pmatrix}\propto PF\begin{pmatrix}1\\2\end{pmatrix}$$

$PF\begin{pmatrix}2\\3\end{pmatrix}\propto C\begin{pmatrix}2\\3\\4\end{pmatrix}$   $A\begin{pmatrix}2\\3\end{pmatrix}\propto PB, PF\rightarrow PF\begin{pmatrix}1\\2\\3\end{pmatrix}$

• Vectorization may be possible with modification, but loop is not concurrent safe

#### What can we do to vectorize this loop?

- Convert PF from a scalar to a vector (1-D array)

- Warning! Be cognizant of how changing this variable may affect other regions of the code

- Is PF a global or local variable? Is the final result of PF used elsewhere?

- May need to use a temporary variable array for the loop and store back into PF if needed

Eliminates the need for the PB scalar variable in the loop

#### Optimization changes

What optimizations did the compiler apply to our new version?

```

66. 1 2

VPF(1) = 0.0

67. 1 2 Vr2--< DO 44031 I = 2, N

68. 1 2 Vr2 AV = B(I) * RV

69. 1 2 Vr2 VPF(I) = C(I)

70. 1 2 Vr2 IF ((D(I) + D(I+1)) .LT. 0.) VPF(I) = -C(I+1)

71. 1 2 Vr2 AA = E(I) - E(I-1) + F(I) - F(I-1)

72. 1 2 Vr2 1 + G(I) + G(I-1) - H(I) - H(I-1)

73. 1 2 Vr2 BB = R(I) + S(I-1) + T(I) + T(I-1)

74. 1 2 Vr2 1 - U(I) - U(I-1) + V(I) + V(I-1)

75. 1 2 Vr2 2 -W(I) + W(I-1) - X(I) + X(I-1)

76.

1 2 Vr2

A(I) = AV * (AA + BB + VPF(I) - VPF(I-1) + Y(I) - Z(I)) +

A(I)

77. 1 2 Vr2--> 44031 CONTINUE

ftn-6005 ftn: SCALAR LP44030, File = lp44030.f, Line = 67

A loop starting at line 67 was unrolled 2 times.

ftn-6204 ftn: VECTOR LP44030, File = lp44030.f, Line = 67

A loop starting at line 67 was vectorized.

```

How does the performance of this version compare with the original?

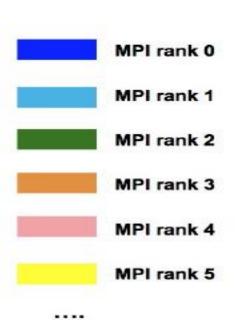

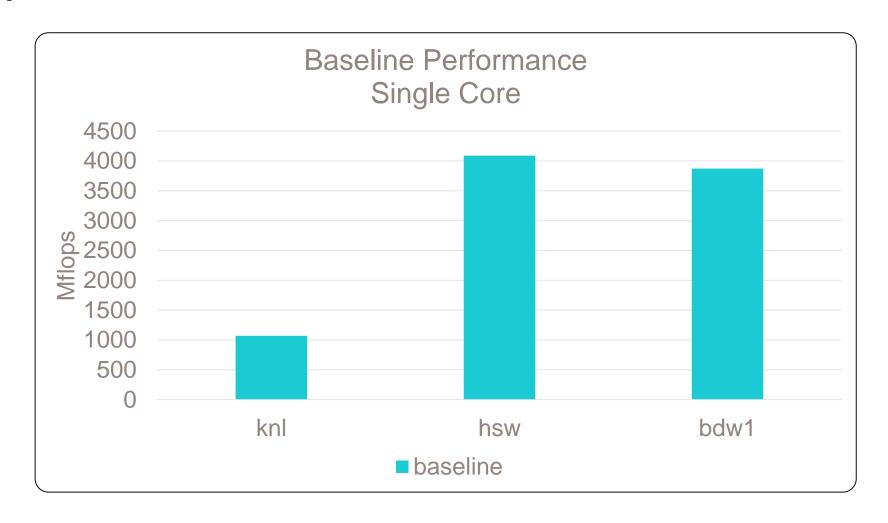

#### Original vs Vectorized performance

# Example Analysis and Optimizations:

Cache blocking

#### Data Reuse will be important

Data reuse will be critical to performance

Reuse out of MCDRAM will reduce requirements on main memory

Reuse out of lower levels of cache will lower requirements on MCDRAM

In order to know how to cache block properly we need to know the trip counts of loops and the sizes of various arrays as accurately as possible

#### A SIMPLE EXAMPLE

2D 5-point Laplacian

- Simple cache structure for this example:

- Assume each cache line holds 4 array elements

- And cache can hold 12 lines of u data

- No cache reuse between outer loop iterations

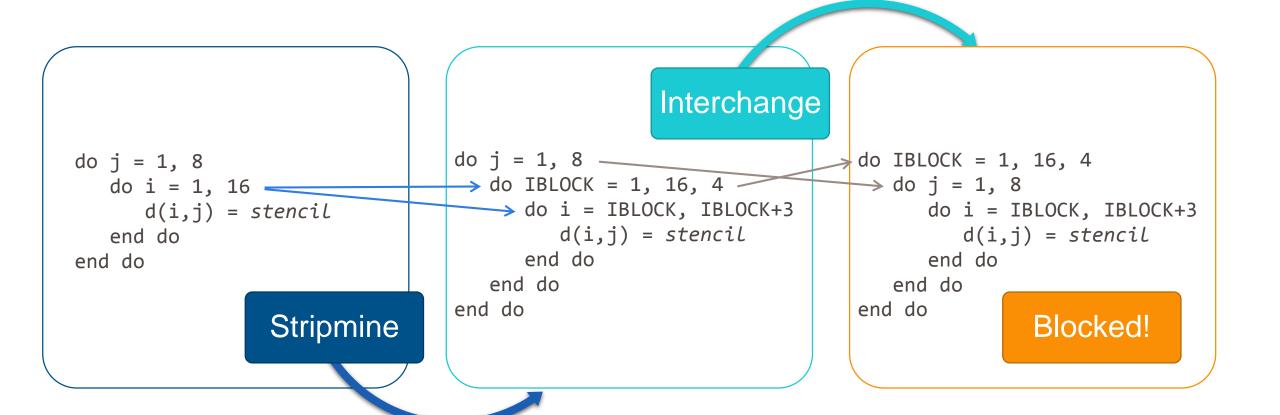

#### BLOCKING = STRIPMINE + INTERCHANGE

#### BLOCKING TO INCREASE REUSE

Block the inner loop

Now we have reuse of the j+1 data

#### **EVEN BETTER!**

Iterate over 4×4 blocks for better spatial locality

- CCE has directives for this

- !dir\$ blockable(i,j)

- !dir\$ blockingsize(4)

# Example Analysis and Optimization:

miniGhost

### Example app: miniGhost

• "mini-app" from the NERSC8 procurement.

27-point 3-D stencil application

Simulates diffusion

- · Like most stencil codes, it is main memory bandwidth bound

- Data reuse will lessen contention for memory accesses

#### Main compute loop

Craypat suggests the following loop is about ~50% of the run time

```

288. + b----<

DO K = 1, NZ

DO J = 1, NY

289. + b b----<

b b Vb----<

DO I = 1, NX

290.

291.

b b Vb

292.

b b Vb

SLICE BACK = GRID(I-1,J-1,K-1) + GRID(I-1,J,K-1) + GRID(I-1,J+1,K-1) + &

293.

b b Vb

GRID(I, J-1, K-1) + GRID(I, J, K-1) + GRID(I, J+1, K-1) + &

294.

b b Vb

GRID(I+1, J-1, K-1) + GRID(I+1, J, K-1) + GRID(I+1, J+1, K-1)

295.

b b Vb

296.

b b Vb

SLICE MINE = GRID(I-1,J-1,K) + GRID(I-1,J,K) + GRID(I-1,J+1,K) + &

GRID(I, J-1,K) + GRID(I, J,K) + GRID(I, J+1,K) + &

297.

b b Vb

298.

b b Vb

GRID(I+1,J-1,K) + GRID(I+1,J,K) + GRID(I+1,J+1,K)

299.

b b Vb

300.

SLICE FRONT = GRID(I-1, J-1, K+1) + GRID(I-1, J, K+1) + GRID(I-1, J+1, K+1) + &

b b Vb

301.

GRID(I , J-1, K+1) + GRID(I , J, K+1) + GRID(I , J+1, K+1) + &

b b Vb

GRID(I+1, J-1, K+1) + GRID(I+1, J, K+1) + GRID(I+1, J+1, K+1)

302.

b b Vb

303.

b b Vb

304.

WORK(I,J,K) = ( SLICE BACK + SLICE MINE + SLICE FRONT ) / 27.0

b b Vb

305.

b b Vb

306.

END DO

b b Vb---->

307.

END DO

308.

END DO

b---->

```

CCE does vectorize and also attempts to cache block the inner loop, but can we do better?

35

#### Listing file explanations

- CCE may attempt to cache block for L2 based upon the targeted architecture.

- Generally, L1 is too small and L3 is too "slow"

```

ftn-6294 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 287

A loop starting at line 287 was not vectorized because a better candidate was found at line 289.

ftn-6049 ftn: SCALAR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 287

A loop starting at line 287 was blocked with block size 8.

ftn-6294 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 288

A loop starting at line 288 was not vectorized because a better candidate was found at line 289.

ftn-6049 ftn: SCALAR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 288

A loop starting at line 288 was blocked with block size 8.

ftn-6049 ftn: SCALAR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 289

A loop starting at line 289 was blocked with block size 256.

ftn-6204 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 289

A loop starting at line 289 was vectorized.

```

#### Blocking = Stripmine + Interchange

```

DO KK = 1, NZ, block k

287. + 1-----

DO JJ = 1, NY, block j

288. + 1 2----<

289. + 1 2 3----<

DO II = 1, NX, block i

290. + 1 2 3 4----< DO K = KK, KK+(block k-1)

291. + 1 2 3 4 5----<

DO J = JJ, JJ+(block j-1)

292. 1 2 3 4 5 V--<

DO I = II, II+(block i-1)

293. 1 2 3 4 5 V

294.

SLICE BACK = GRID(I-1,J-1,K-1) + GRID(I-1,J,K-1) + GRID(I-1,J+1,K-1) + &

1 2 3 4 5 V

295.

1 2 3 4 5 V

GRID(I ,J-1,K-1) + GRID(I ,J,K-1) + GRID(I ,J+1,K-1) + &

296.

GRID(I+1, J-1, K-1) + GRID(I+1, J, K-1) + GRID(I+1, J+1, K-1)

1 2 3 4 5 V

297.

1 2 3 4 5 V

298.

1 2 3 4 5 V

SLICE MINE = GRID(I-1,J-1,K) + GRID(I-1,J,K) + GRID(I-1,J+1,K) + &

GRID(I, J-1, K) + GRID(I, J, K) + GRID(I, J+1, K) + &

1 2 3 4 5 V

299.

GRID(I+1, J-1, K) + GRID(I+1, J, K) + GRID(I+1, J+1, K)

300.

1 2 3 4 5 V

301.

1 2 3 4 5 V

302.

SLICE FRONT = GRID(I-1,J-1,K+1) + GRID(I-1,J,K+1) + GRID(I-1,J+1,K+1) + &

1 2 3 4 5 V

1 2 3 4 5 V

GRID(I ,J-1,K+1) + GRID(I ,J,K+1) + GRID(I ,J+1,K+1) + &

303.

GRID(I+1, J-1, K+1) + GRID(I+1, J, K+1) + GRID(I+1, J+1, K+1)

304.

1 2 3 4 5 V

305.

1 2 3 4 5 V

1 2 3 4 5 V

WORK(I, J, K) = ( SLICE BACK + SLICE MINE + SLICE FRONT ) / 27.0

306.

307.

1 2 3 4 5 V

308.

1 2 3 4 5 V-->

END DO

309.

1 2 3 4 5--->

END DO

310.

1 2 3 4---->

END DO

311. 1 2 3---->

END DO

312. 1 2----> END DO

313. 1----->

END DO

```

#### Listing file explanations

```

ftn-6306 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 287

A loop starting at line 287 was not vectorized because the iteration space is too irregular.

ftn-6306 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 288

A loop starting at line 288 was not vectorized because the iteration space is too irregular.

ftn-6303 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 289

A loop starting at line 289 was not vectorized because an inter-loop dependence relation is too complicated.

ftn-6303 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 290

A loop starting at line 290 was not vectorized because an inter-loop dependence relation is too complicated.

ftn-6303 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 291

A loop starting at line 291 was not vectorized because an inter-loop dependence relation is too complicated.

ftn-6204 ftn: VECTOR MG STENCIL 3D27PT, File = MG STENCIL COMPS.F, Line = 292

A loop starting at line 292 was vectorized.

```

#### How to set the correct block sizes

- Typically, you want a larger amount of the inner iteration with smaller amounts in the other loops

- Depends on the loop characterization and what data should be / could be / need to be reused

- Powers of 2 generally are best if full index can not be held in cache

- Depending on the particular problem size, a proper cache blocking can provide a 50% speed-up for this particular loop on KNL

- May see smaller impact on earlier Xeon processors since L2 misses are supported by an L3 cache.

#### Summary

- Code Characterization is an important first step in preparing for KNL

- Target Science

- Target Scaling

- Hotspot identification

- Process affinity is critical for run performance

- Statically linked binaries likely to perform better than dynamically linked binaries.

- KNL node is different from XEON node

- Single node optimizations will be an early focus

- A properly designed kernel will help with optimization efforts

- Vectorization is important and will become even more so with future processors

Data reuse is important, but how important will depend on memory footprints and access patterns

## THANK YOU

QUESTIONS?